Gernot Hoyler Spansion Inc.

Pre-silicon Software Development of Linux MTD Drivers

**October 30, 2009**

• FLASH FORWARD

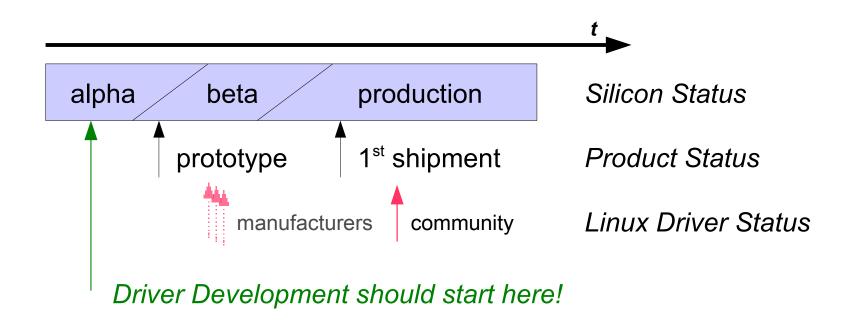

### **Product Development Process**

Ideally, device drivers are already available when customers get their hands on first samples. A simulator based approach can help work around hardware issues that might exist during this early phase (alpha phase).

#### **Flash Basics**

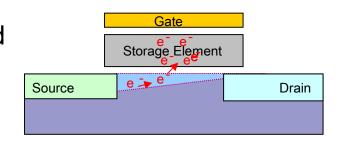

Electrical charge is moved onto an isolated storage element in order to *program* data (done on a bit basis for NOR flash or on a page basis for NAND flash)

- Electrical charge is removed from the isolated area in order to erase data (done on a sector/block basis, e.g. 128 kB)

- To read data, a reference voltage is applied between source and drain and the current is measured (if current flows, the cell has been programmed)

- A special command set is being used to issue and to control the program and erase operations

# **S29WS-R Command Set**

|   | 0   | , |

|---|-----|---|

| 0 | 000 | 6 |

| 0 | W.  | 6 |

| - | -   |   |

| 0 | 0   | 6 |

|   |     |   |

|                       |                       |        | Bus Cycles (Notes 1–5) |          |                      |           |                      |      |                      |      |

|-----------------------|-----------------------|--------|------------------------|----------|----------------------|-----------|----------------------|------|----------------------|------|

|                       |                       | 8      | First                  |          | Second               |           | Third                |      | Fourth               |      |

|                       | Command Sequence      | Cycles | Addr<br>Byte<br>Word   | Data     | Addr<br>Byte<br>Word | Data      | Addr<br>Byte<br>Word | Data | Addr<br>Byte<br>Word | Data |

| Read                  |                       | 1      | RA                     | RD       |                      |           |                      |      |                      |      |

| Reset                 |                       | 1      | XX                     | F0       |                      |           |                      |      |                      |      |

| Write Buffer Load (9) |                       | 4-35   | (SA) AAA<br>(SA) 555   | 25       | (SA) 555<br>(SA) AAA | WC        | (SA) PA (12)         | PD   | (SA) PA (13)         | PD   |

| Buffer to Flash       |                       | 1      | (SA) AAA<br>(SA) 555   | 29       |                      |           |                      |      |                      |      |

| Chip Erase            |                       | 2      | (SA) AAA<br>(SA) 555   | 80       | (SA) 555<br>(SA) AAA | 10        |                      |      |                      |      |

| Sector Erase          |                       | 2      | (SA) AAA<br>(SA) 555   | 80       | (SA) 555<br>(SA) AAA | 30        |                      |      |                      |      |

| Status Register Read  |                       | 2      | (SA) AAA<br>(SA) 555   | 70       | (SA)                 | RR        |                      |      |                      |      |

| Status Register Clear |                       | 1      | (SA) AAA<br>(SA) 555   | 71       |                      |           |                      |      |                      |      |

|                       |                       |        |                        | ID/CF    | l Command De         | finitions | 1                    |      | ,                    |      |

| ID/CFI                | ID/CFI Entry (8) (11) | 1      | (SA) XAA<br>(SA) X55   | 90 or 98 |                      |           |                      |      |                      |      |

|                       | ID/CFI Read           | 1      | (SA) RA                | data     |                      |           |                      |      |                      |      |

|                       | ID/CFI Exit           | 1      | XXX                    | F0       |                      |           |                      |      |                      |      |

. . .

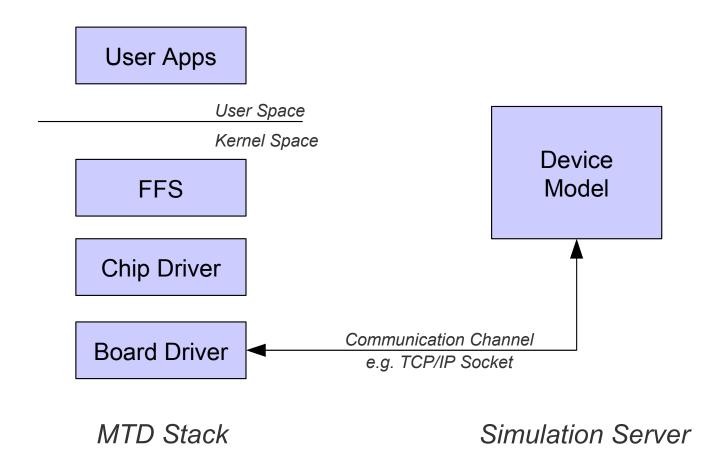

#### **Simulator Based Approach for MTD Drivers**

#### **Device Model / Simulation Server**

# DevSim is a cycle accurate SystemC model of Spansion Flash. It supports the following formats:

- DevSim object for Cadence Design Systems' NC-Verilog on Linux

- DevSim object for Synopsys' VCS on Linux

- DevSim object for Microsoft Visual Studio

- DevSim executable/server and command line client

#### Benefits:

- Developed by Spansion for internal verification

- Cycle accurate

- Detects and reports timing violations

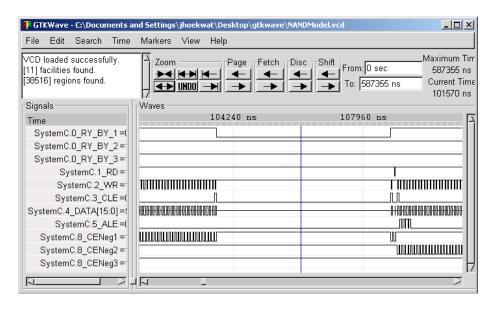

- Creates a waveform of the session

- •Resource sensitive Simulates as much of the array as you use

- Truly non-volatile from session to session

- View the array outside of a session

- Array pre-loading supported

- •Flash architecture controlled by CFI input file

- ·Works great for software development

- •Program and erase times can be altered to reduce real-time execution

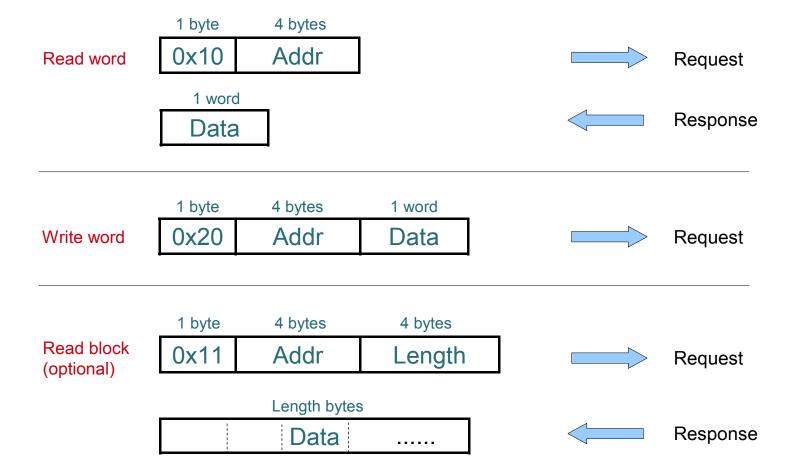

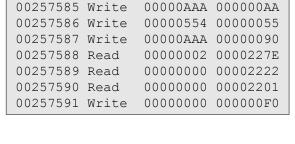

#### **Communication Channel Protocol**

### **MTD** Board or Map Driver

The pivotal element connecting a chip driver (NOR flash) to the hardware is a map info, see include/linux/mtd/map.h

```

struct map info {

char *name;

Function pointers to issue read &

unsigned long size;

write cycles to the flash device

resource size t phys;

void iomem *virt;

void *cached;

int bankwidth;

map word (*read) (struct map info *, unsigned long);

void (*write)(struct map info *, const map word, unsigned long);

void (*copy from)(struct map info *, void *, unsigned long, ssize t);

void (*copy to)(struct map info *, unsigned long, const void *, ssize t);

void (*inval cache)(struct map info *, unsigned long, ssize t);

void (*set vpp) (struct map info *, int);

};

```

All the driver has to implement are functions that route the r/w requests over the communication channel to the model.

# **Proper Synchronization**

- Replacing the standard I/O calls used for a physical device

(\_\_raw\_readw(), \_\_raw\_writew()) by socket calls changes the

characteristics of the I/O from non-blocking to blocking.

- This can cause issues if the kernel holds spin-locks during the I/O.

Another thread trying to acquire the spin-lock at the same time can stall the entire system (deadlock).

- Some MTD chip drivers hold a spin-lock while issuing commands.

This spin-lock needs to be released before the socket operations take place and reacquired afterwards.

- To prevent other threads from accessing the MTD while the socket operations are ongoing, the device has to be put into a special mode so that other threads have to wait, i.e. sleep and try again later.

#### **Live Demo**

```

000

```

```

gernot@MUC-N-0037:/home/gernot/FlashModel Projects/Syst

File Edit View Terminal Help

Read.

address: 0x000000aa, data: 0x0008

Read.

address: 0x000000ac. data: 0x0008

address: 0x000000ae, data: 0x0010

Read.

Write, address: 0x00000000, data: 0x00f0 *

Write, address: 0x00000000, data: 0x00ff *

Write, address: 0x00000aaa, data: 0x0071 *

gernot@MUC-N-0037:/home/gernot/devsim_mtd_nor

Σ

_ + X

File Edit View Terminal Help

[root@MUC-N-0037 devsim mtd nor]#

[root@MUC-N-0037 devsim mtd nor]# insmod devsim.ko

[root@MUC-N-0037 devsim mtd nor]# Oct 22 13:37:18 MUC-N-0037 kernel: DevSim initialization...

Oct 22 13:37:18 MUC-N-0037 kernel: DevSim NOR flash 16-bit: Found 1 x16 devices at 0x0 in 16-

bit bank

Oct 22 13:37:18 MUC-N-0037 kernel: Spansion Extended Query Table at 0x0040

Oct 22 13:37:18 MUC-N-0037 kernel: number of CFI chips: 1

Oct 22 13:37:18 MUC-N-0037 kernel: Creating 1 MTD partitions on "DevSim NOR flash 16-bit":

Oct 22 13:37:18 MUC-N-0037 kernel: 0x00000000000-0x000000100000 : "DevSim Partition 1"

[root@MUC-N-0037 devsim mtd nor]# flash erase /dev/mtd0

Erase Total 1 Units

Performing Flash Erase of length 131072 at offset 0x0 done

[root@MUC-N-0037 devsim mtd nor]#

```

# **Further Advantages**

Next to the early availability, a simulator based approach has further advantages:

- √ Simplified debugging

- ✓ Software trace support (virtual logic analyzer)

- Errors can easily be inserted

- ✓ Different device models can be loaded quickly

- ✓ Non-standard bus widths and setups can easily be tested

✓ Spec violation checks can be added

Type

Sync

Address

32-bit cascaded

Data

# **Summary**

- A new approach for pre-silicon software development of MTD chip drivers has been proposed

- In the context of the development of a new NOR flash driver it proved to be stable and beneficial

- It can be used not only at an early stage where no Si is available yet, it also greatly simplifies testing and debugging

- A similar approach should be conceivable for other memory technologies such as NAND or SPI devices

- All it needs is to route the flash specific interface over a communication channel to a device model

# **Thank You!**

#### **Trademark Attribution**

Spansion®, the Spansion logo, MirrorBit®, MirrorBit® Eclipse™, ORNAND™, ORNAND2™, HD-SIM™ and combinations thereof, are trademarks of Spansion LLC in the U.S. and other countries. Other names used are for informational purposes only and may be trademarks of their respective owners.

This document is for informational purposes only and subject to change without notice. Spansion does not represent that it is complete, accurate or up-to-date; it is provided "AS IS." To the maximum extent permitted by law, Spansion disclaims any liability for loss or damages arising from use of or reliance on this document.